## СОДЕРЖАНИЕ 1.1 Архитектурные особенности микросхемы ....... 6 Инв. № дубл. 3.7.3 Регистры контроллера GPIO .......51 3.8 Контроллер интерфейса последовательного UHB. Взам. Подп. и дата Версия 2.04 от 01.09.2017 г. Изм. Лист № докум. Подп. Дата Разраб. Лист Лит Листов Микросхема интегральная нв. № подл. Пров. 259 5023BC016. Н. контр. Техническое описание Утв.

|               |                               | 3.8.5 Общие регистры настроек                                      | 61         |  |  |  |  |  |  |

|---------------|-------------------------------|--------------------------------------------------------------------|------------|--|--|--|--|--|--|

|               |                               | 3.8.6 Регистры монитора                                            | 63         |  |  |  |  |  |  |

|               |                               | 3.8.7 Peгистр INTERRUPT                                            | 64         |  |  |  |  |  |  |

|               |                               | 3.8.8 Описание функционирования контроллера последовательного инт  | ерфейса по |  |  |  |  |  |  |

|               |                               | ΓΟCT P 52070                                                       | 64         |  |  |  |  |  |  |

|               |                               | 3.9 Контроллер интерфейса SpaceWire                                | 72         |  |  |  |  |  |  |

|               |                               | 3.9.1 Описание функционирования контроллера интерфейса SpaceWire . | 72         |  |  |  |  |  |  |

|               |                               | 3.9.2 Контроллер BUS MASTER                                        | 75         |  |  |  |  |  |  |

|               |                               | 3.9.3 Регистры контроллера интерфейса SpaceWire                    | 76         |  |  |  |  |  |  |

|               |                               | 3.10 Контроллер прямого доступа к памяти                           | 80         |  |  |  |  |  |  |

|               |                               | 3.10.1 Общее описание                                              | 80         |  |  |  |  |  |  |

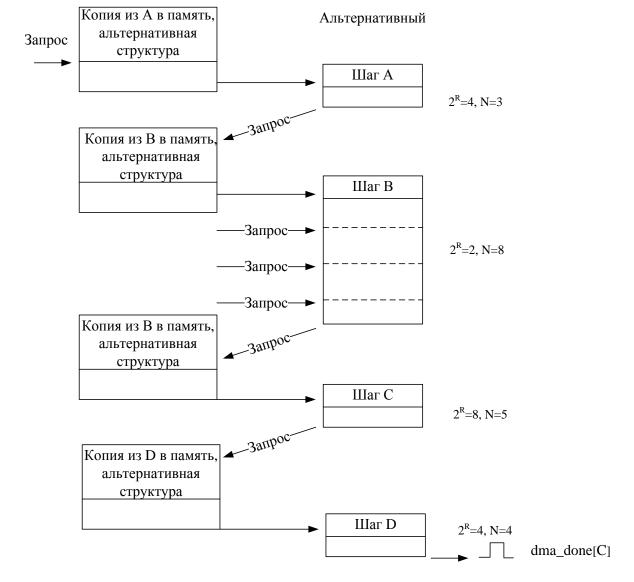

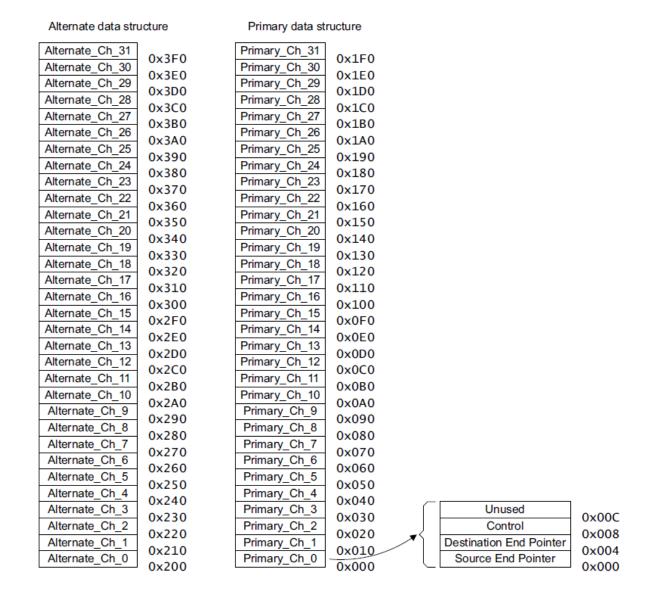

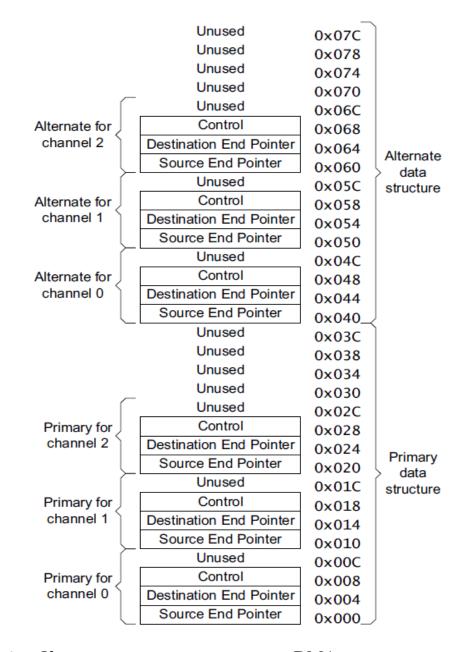

|               |                               | 3.10.2 Описание функционирования контроллера DMA                   | 81         |  |  |  |  |  |  |

|               |                               | 3.10.3 Программное управление модулем                              | 98         |  |  |  |  |  |  |

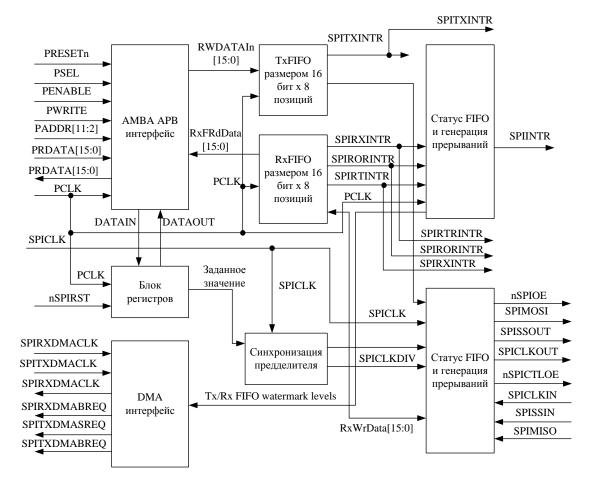

|               |                               | 3.11 Контроллер интерфейса SPI                                     | 127        |  |  |  |  |  |  |

|               |                               | 3.11.1 Общие положения                                             | 127        |  |  |  |  |  |  |

|               |                               | 3.11.2 Основные характеристики интерфейса SPI                      | 128        |  |  |  |  |  |  |

| Γ             |                               | 3.11.3 Программируемые параметры интерфейса SPI                    | 128        |  |  |  |  |  |  |

| <br>          |                               | 3.11.4 Характеристики интерфейса SPI фирмы Motorola                |            |  |  |  |  |  |  |

| и дата.       |                               | 3.11.5 Функциональное описание интерфейса SPI                      | 130        |  |  |  |  |  |  |

| Подп. ц       |                               | 3.11.6 Функционирование модуля SPI                                 | 132        |  |  |  |  |  |  |

|               |                               | 3.11.7 Интерфейс прямого доступа к памяти                          |            |  |  |  |  |  |  |

| дубл          |                               | 3.11.8 Программное управление модулем                              | 149        |  |  |  |  |  |  |

| Инв. Nº дубл. |                               | 3.11.9 Прерывания модуля                                           | 156        |  |  |  |  |  |  |

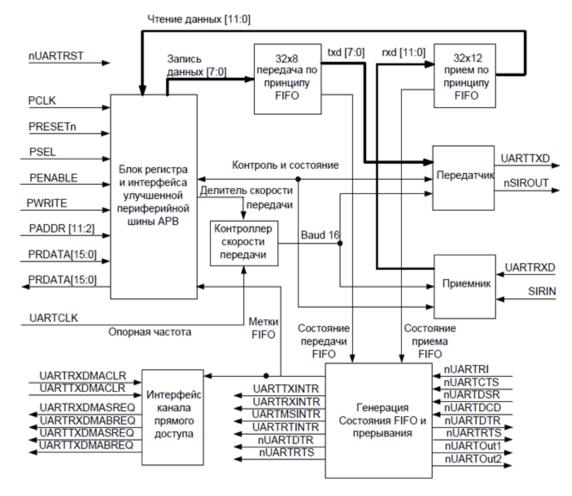

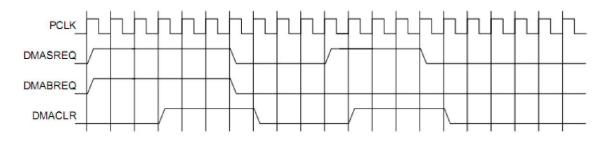

|               | ┢                             | 3.12 Контроллер интерфейса UART                                    | 158        |  |  |  |  |  |  |

| лнв. Л        |                               | 3.12.1 Общие положения                                             |            |  |  |  |  |  |  |

| Взам. инв. №  |                               | 3.12.2 Основные характеристики интерфейса UART                     | 158        |  |  |  |  |  |  |

| В             |                               | 3.12.3 Описание функционирования интерфейса UART                   | 162        |  |  |  |  |  |  |

|               |                               | 3.12.4 Описание функционирования модуля UART                       |            |  |  |  |  |  |  |

| ama           |                               |                                                                    |            |  |  |  |  |  |  |

| Подп. и дата  |                               |                                                                    |            |  |  |  |  |  |  |

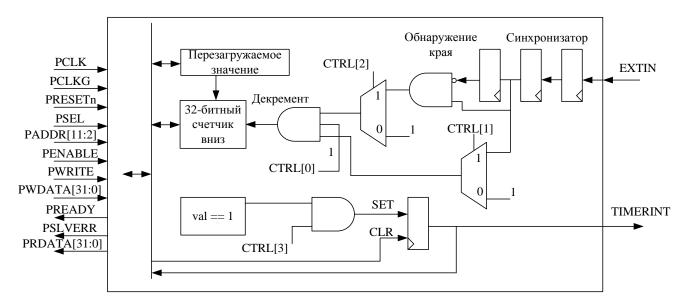

| _             | 3.13 Таймер общего назначения |                                                                    |            |  |  |  |  |  |  |

| Инв. № подл.  |                               | Minima avana in mara ana ana ana ana ana ana ana ana ana           | In.        |  |  |  |  |  |  |

| '8. Nº        |                               | Микросхема интегральная 5023BC016<br>Техническое описание          | Лисп       |  |  |  |  |  |  |

| $\vec{z}$     |                               | 1зм Лист № докум. Подп. Дата Версия 2.04 om 01.09.2017 г.          | 3          |  |  |  |  |  |  |

| 3.13.1 Общее описание                                                | 192      |

|----------------------------------------------------------------------|----------|

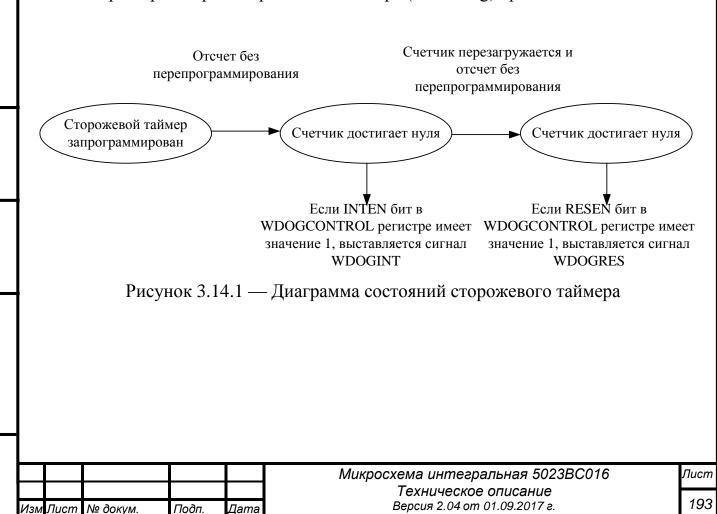

| 3.14 Сторожевой таймер                                               |          |

| 3.14.1 Описание сторожевого таймера                                  |          |

| 3.14.2 Регистры сторожевого таймера (Watchdog)                       |          |

| 3.15 Передатчик телеметрической информации                           |          |

| 3.15.1 Описание структуры передатчика телеметрической информации     |          |

| 3.15.2 Описание работы интерфейса передатчика телеметри              |          |

| информации                                                           |          |

| 3.15.3 Программная модель управления передатчиком телеметри          |          |

| информации                                                           |          |

| 3.15.4 Регистры передатчика телеметрической информации               |          |

| 3.16 Приёмник телекомандной информации                               |          |

| 3.16.1 Общее описание приёмника телекомандной информации             |          |

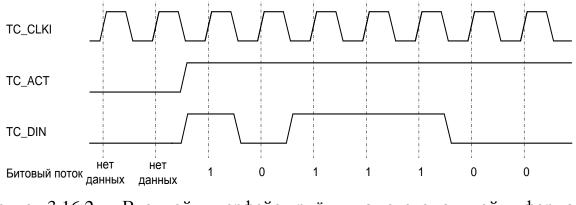

| 3.16.2 Описание работы интерфейса приёмника телекомандной информации |          |

| 3.16.3 Программная модель управления приёмником телеком              |          |

| информации                                                           |          |

| 3.16.4 Описание регистров приёмника телекомандной информации         |          |

| 3.17 Специализированный вычислитель с плавающей точкой               |          |

| 3.17.1 Описание регистров                                            |          |

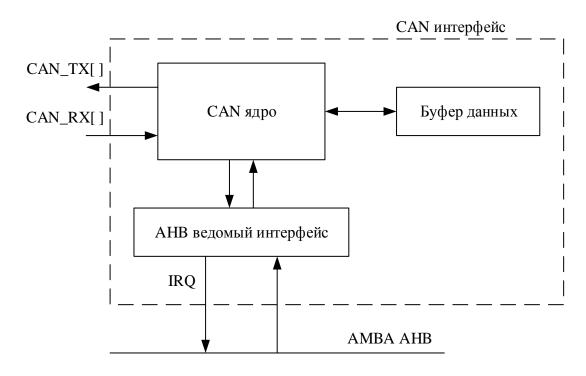

| 3.18 Контроллер интерфейса CAN                                       |          |

| 3.18.1 Общее описание                                                | 225      |

| 3.18.2 Базовый режим работы                                          | 226      |

| 3.18.3 Расширенный режим работы                                      | 231      |

| 3.18.4 Общие регистры для базового и расширенного режимов работы     | 243      |

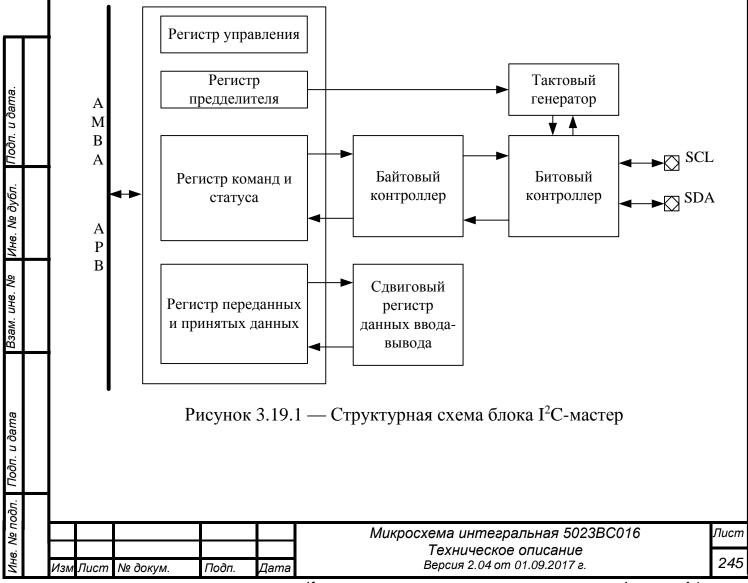

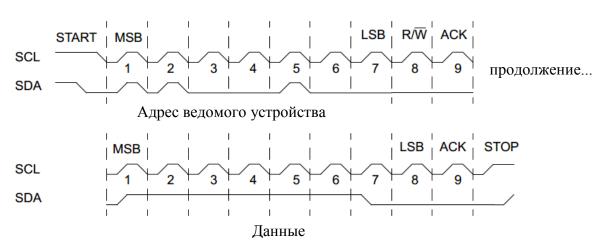

| 3.19 Контроллер интерфейса I <sup>2</sup> C                          | 245      |

| 3.19.1 Описание работы блока I <sup>2</sup> C-мастер                 | 246      |

| 3.19.2 Описание регистров блока I <sup>2</sup> C-мастер              | 252      |

| Перечень сокращений и условных обозначений                           | 255      |

| Перечень ссылочных документов                                        | 257      |

| Перечень изменений                                                   | 258      |

|                                                                      |          |

|                                                                      | <u> </u> |

| Микросхема интегральная 5023BC016<br>Техническое описание            | Лисп     |

| Изм Лист № докум. Подп. Дата Версия 2.04 om 01.09.2017 г.            | 4        |

Инв. № подл. Подп. и дата

#### Введение

Настоящее техническое описание распространяется на интегральную микросхему 5023ВС016 (далее — микросхема СБИС СРU), предназначенную для применения в качестве специализированной схемы обработки информации в радиоэлектронной аппаратуре специального назначения.

Радиационно-стойкая специализированная микросхема 5023BC016 предназначена для построения аппаратуры контрольно-измерительных систем (КИС), телеметрии служебных систем космических аппаратов с учетом эксплуатации их в жестких условиях специальных видов воздействующих факторов.

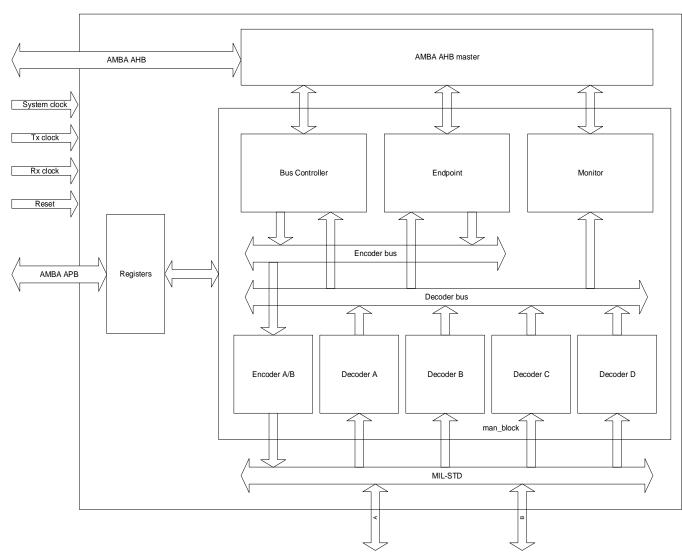

Микросхема может использоваться для организации каналов связи по интерфейсам магистральной последовательной шины по ГОСТ Р 52070 с резервированием.

При этом микросхема может использоваться в качестве контроллера шины (КШ), оконечного устройства (ОУ), а также монитора.

Наличие двух контроллеров интерфейсов SpaceWire со скоростью передачи данных до 100 Мбит/с позволяет использовать микросхему в каналах передачи данных данного типа.

Микросхема имеет блоки передатчика телеметрической информации и приёмника телекомандной информации, позволяющие использовать различные виды кодирования (LDPC, Турбо, Рида-Соломона).

Применение микросхемы позволяет создавать системы управления космическими аппаратами совместимыми с международными стандартами CCSDS, уменьшить массогабаритные характеристики и потребляемую мощность аппаратуры КИС, телеметрии служебных систем космических аппаратов в 4 – 5 раз и обеспечить требования Федерального космического агентства по дозовой стойкости и воздействию тяжелых заряженных частиц.

Iнв. № подл. Подп. и дата Взам. инв. № Инв. № дубл. Подп. и дв

Изм Лист № докум. Подп. Дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 от 01.09.2017 г.

## 1 Назначение и основные технические характеристики

#### 1.1 Архитектурные особенности микросхемы

Интегральная микросхема 5023ВС016 представляет собой однокристальный 32 разрядный процессор, выполненный по КМОП технологии с нормами 0,18 мкм. Микросхема предназначена для построения аппаратуры КИС, телеметрии служебных систем космических аппаратов с учетом эксплуатации их в жестких условиях специальных видов воздействующих факторов.

Основные функциональные параметры микросхемы:

| разрядность шины адреса ядра процессора       | 32 бита    |

|-----------------------------------------------|------------|

| конвейер                                      | 3 стадии   |

| аппаратный умножитель                         | 32 x 32    |

| тип встроенной шины                           | AMBA       |

| размер встроенного оперативного запоминающего |            |

| устройства (ОЗУ)                              | 128 κΒ     |

| тактовая частота, МГц                         | 501)       |

| напряжение питания ядра, В                    | 1,8 ± 10 % |

| напряжение питания буферов ввода-вывода, В    | 3,3 ± 10 % |

| СБИС СРИ включает следующие основные блоки:   |            |

- а) ядро 32-битного Reduced Instruction Set Computer (RISC) процессора;

- б) четыре независимых контроллера последовательного интерфейса по ГОСТ Р 52070 с резервированием;

- в) два независимых контроллера интерфейса SpaceWire со скоростью передачи данных до 100 Мбит/с;

- г) контроллер прямого доступа к памяти;

Инв. № дубл.

Взам. инв. №

Подп. и дата

д) внутрикристальную схему отладки с интерфейсом Joint Test Action Group (JTAG) (IEEE 1149.1);

$<sup>^{1)}</sup>$  Возможна работа на тактовой частоте  $80\,\mathrm{MF}$ ц. При этом значения динамического тока потребления ядра для основных режимов работы микросхемы приведены в таблице 1.3.3.

|     |      |          |       |      | Микросхема интегральная 5023ВС016 | Лист |

|-----|------|----------|-------|------|-----------------------------------|------|

|     |      |          |       |      | Техническое описание              |      |

| Изм | Лист | № докум. | Подп. | Дата | Версия 2.04 от 01.09.2017 г.      | 6    |

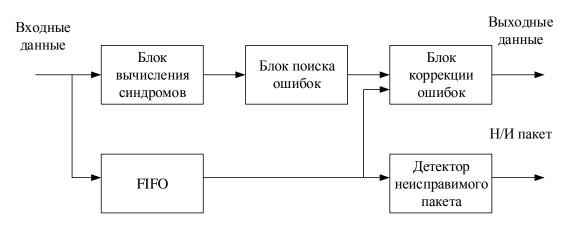

ж) контроллер внешней памяти со встроенным блоком обнаружения и исправления ошибок, с поддержкой до четырех микросхем внешней памяти и с поддержкой кэширования;

- 3) шесть независимых контроллеров асинхронного последовательного интерфейса Universal asynchronous receiver-transmitter (UART);

- и) два независимых контроллера последовательного интерфейса Serial Perepheral Interface (SPI);

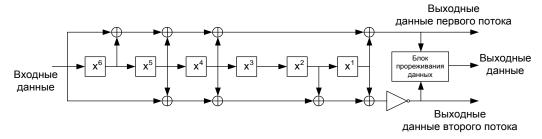

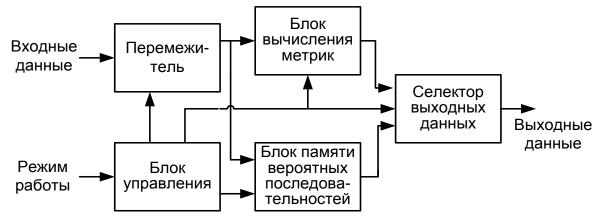

- к) контроллер приёмника телекомандной информации (ПрТКИ) по стандарту Consultative Committee for Space Data Systems (CCSDS), включающий следующие блоки:

- 1) декодер БЧХ (63,56) размер блока 63 бита, размер полезных данных 56 бит;

- 2) декодер Витерби;

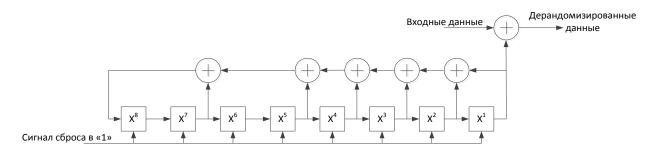

- 3) дерандомизатор;

Инв. № дубл.

Взам. инв. №

Подп. и дата

нв. № подл.

- л) контроллер передатчика телеметрической информации (ПдТМИ) по стандарту CCSDS, включающий следующие блоки:

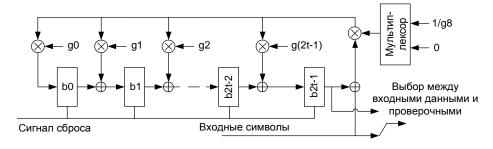

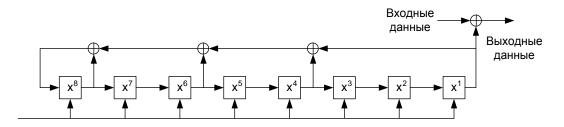

- 1) энкодер Рида-Соломона с параметрами (N = 255, K = 223), (N = 255, K = 239) размер блока 255 символов, размер полезных данных 223 или 239 символов, разрядность 8 бит, порождающий полином  $F(x) = x^8 + x^7 + x^2 + x + 1$ ;

- 2) турбо энкодер со скоростью кодирования (отношению объёма полезных данных к объёму передаваемых) 1/2, 1/3, 1/4, 1/6;

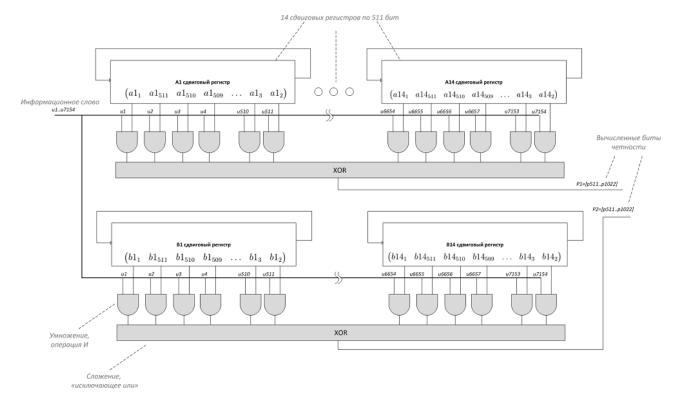

- 3) LDPC энкодер с параметрами (8160, 7136) (размер кодового блока 8160 символов, размер блока данных 7136 символов);

- 4) сверточный энкодер со скоростью кодирования (отношению объема полезных данных к объему передаваемых) 1/2, 2/3, 3/4, 5/6 или 7/8, разрядность 7 бит, порождающие полиномы: G1 = 1111001, G2 = 1011011;

- 5) рандомизатор;

| Микросхема интегральная 5023BC016<br>Техническое описание |      |

|-----------------------------------------------------------|------|

| Теунциеское описание                                      | Лист |

|                                                           | _    |

| Изм Лист № докум. Подп. Дата Версия 2.04 om 01.09.2017 г. | /    |

Копировал

Формат А4

- б) формирователь кадров;

- м) два независимых контроллера интерфейса Controller Area Network (CAN);

- н) контроллер интерфейса I<sup>2</sup>C в режиме мастера;

- о) специализированный вычислитель с плавающей точкой.

- 1.2 Конструктивные параметры микросхемы

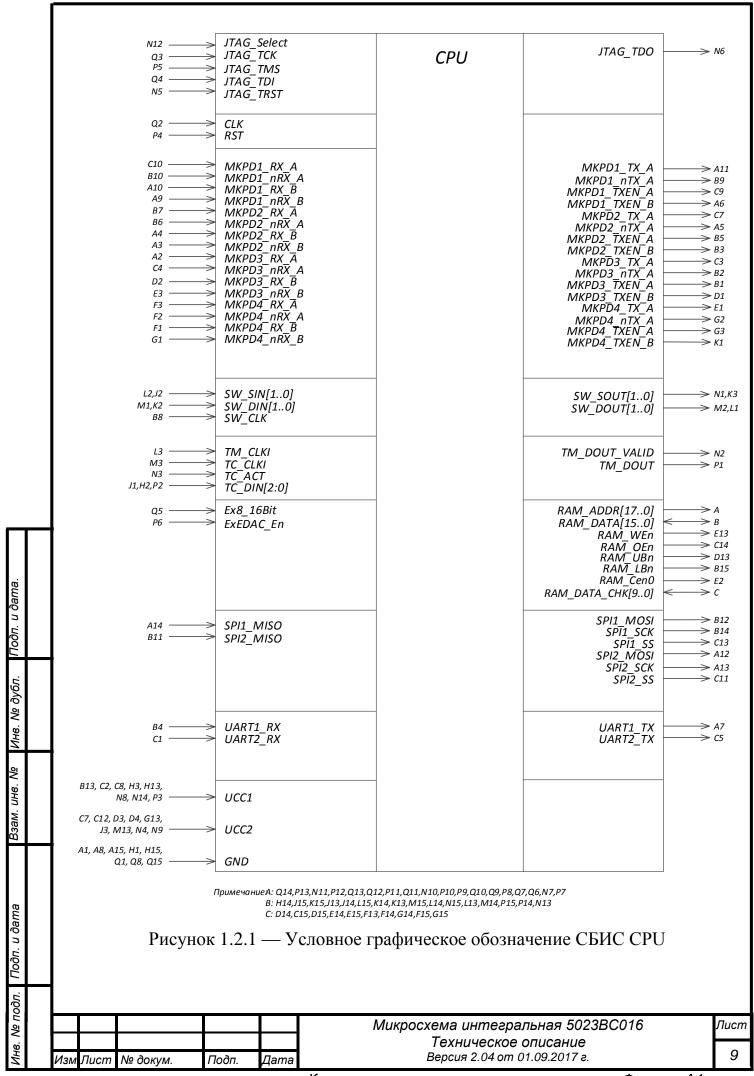

Функциональное назначение выводов микросхемы приведено в таблице 1.2.1.

Микросхема выполнена в металлокерамическом корпусе 6112.145-1 и предназначена для ручной и автоматической сборки в соответствии с ГОСТ В 20.39.412.

Масса микросхемы не более 20 г.

Значение собственной резонансной частоты не менее 3,6 кГц.

Предельная повышенная температура среды плюс 125 °C.

Показатель герметичности микросхем со свободным внутренним объёмом по эквивалентному нормализованному потоку не более  $6,65\cdot10^{-3}$  Па·см<sup>3</sup>/с.

Более подробно конструктивные характеристики микросхемы приведены в технических условиях AEЯР.431290.994 ТУ.

Условное графическое обозначение микросхемы приведено на рисунке 1.2.1.

нв. № подл. и дата Взам. инв. № Инв. № дубл. Подп. и дат

13м Лист № докум. Подп. Дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 от 01.09.2017 г. Лист

8

Таблица 1.2.1 — Функциональное назначение выводов

Название вывода

GND

Номер вывода

**A**1

Инв. № дубл.

Взам. инв. №

Подп. и дата

1нв. № подл.

| 111 | GND          | Оощии        |            |

|-----|--------------|--------------|------------|

| A2  | MKPD3_RX_A   | Вход/выход   | GPIO_F(4)  |

| A3  | MKPD2_nRX_B  | Вход/выход   | GPIO_F(2)  |

| A4  | MKPD2_RX_B   | Вход/выход   | GPIO_F(1)  |

| A5  | MKPD2_nTX_A  | Вход/выход   | GPIO_E(15) |

| A6  | MKPD1_TXEN_B | Вход/выход   | GPIO_E(11) |

| A7  | UART1_TxD    | Вход/выход   | GPIO_D(15) |

| A8  | GND          | Общий        | Питание    |

| A9  | MKPD1_nRX_B  | Вход/выход   | GPIO_E(10) |

| A10 | MKPD1_RX_B   | Вход/выход   | GPIO_E(9)  |

| A11 | MKPD1_TX_A   | Вход/выход   | GPIO_E(6)  |

| A12 | SPI2_MOSI    | Вход/выход   | GPIO_D(14) |

| A13 | SPI2_SCK     | Вход/выход   | GPIO_D(12) |

| A14 | SPI1_MISO    | Вход/выход   | GPIO_D(9)  |

| A15 | GND          | Общий        | Питание    |

| B1  | MKPD3_TXEN_A | Вход/выход   | GPIO_F(8)  |

| B2  | MKPD3_nTX_A  | Вход/выход   | GPIO_F(7)  |

| В3  | MKPD2_TXEN_B | Вход/выход   | GPIO_F(3)  |

| B4  | UART1_RxD    | Вход/выход   | GPIO_E(0)  |

| B5  | MKPD2_TXEN_A | Вход/выход   | GPIO_F(0)  |

| B6  | MKPD2_nRX_A  | Вход/выход   | GPIO_E(13) |

| B7  | MKPD2_RX_A   | Вход/выход   | GPIO_E(12) |

| B8  | SW_CLK       | Вход/выход   | GPIO_H(4)  |

| B9  | MKPD1_nTX_A  | Вход/выход   | GPIO_E(7)  |

| B10 | MKPD1_nRX_A  | Вход/выход   | GPIO_E(5)  |

| B11 | SPI2_MISO    | Вход/выход   | GPIO_D(13) |

| B12 | SPI1_MOSI    | Вход/выход   | GPIO_D(10) |

| B13 | VCC1         | Питание UCC1 | Питание    |

Тип вывода

3

Общий

Изм Лист № докум. Подп. Дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 от 01.09.2017 г.

10

Номер соответствующего порта

ввода-вывода/функция

Питание

| 1   | 2               | 3                | 4                  |

|-----|-----------------|------------------|--------------------|

| B14 | SPI1_SCK        | Вход/выход       | GPIO_D(8)          |

| B15 | RAM_Lbn         | Вход/выход       | GPIO_D(5)          |

| C1  | UART2_RX        | Вход/выход       | GPIO_E(1)          |

| C2  | VCC1            | Питание UCC1     | Питание            |

| C3  | MKPD3_TX_A      | Вход/выход       | GPIO_F(6)          |

| C4  | MKPD3_nRX_A     | Вход/выход       | GPIO_F(5)          |

| C5  | UART2_TX        | Вход/выход       | GPIO_E(2)          |

| C6  | MKPD2_TX_A      | Вход/выход       | GPIO_E(14)         |

| C7  | VCC2            | Питание UCC2     | Питание            |

| C8  | VCC1            | Питание UCC1     | Питание            |

| C9  | MKPD1_TXEN_A    | Вход/выход       | GPIO_E(8)          |

| C10 | MKPD1_RX_A      | Вход/выход       | GPIO_E(4)          |

| C11 | SPI2_SS         | Вход/выход       | GPIO_D(11)         |

| C12 | VCC2            | Питание UCC2     | Питание            |

| C13 | SPI1_SS         | Вход/выход       | GPIO_D(7)          |

| C14 | RAM_Oen         | Вход/выход       | GPIO_D(4)          |

| C15 | RAM_DATA_CHK(8) | Вход/выход       | GPIO_D(0)          |

| D1  | MKPD3_TXEN_B    | Вход/выход       | GPIO_F(11)         |

| D2  | MKPD3_RX_B      | Вход/выход       | GPIO_F(9)          |

| D3  | VCC2            | Питание UCC2     | Питание            |

| D4  | VCC2            | Питание UCC2     | Питание            |

| D13 | RAM_Ubn         | Вход/выход       | GPIO_D(6)          |

| D14 | RAM_DATA_CHK(9) | Вход/выход       | GPIO_D(1)          |

| D15 | RAM_DATA_CHK(7) | Вход/выход       | GPIO_C(15)         |

| E1  | MKPD4_TX_A      | Вход/выход       | GPIO_F(14)         |

| E2  | RAM_Cen0        | Вход/выход       | GPIO_E(3)          |

| E3  | MKPD3_nRX_B     | Вход/выход       | GPIO_F(10)         |

| E13 | RAM_Wen         | Вход/выход       | GPIO_D(2)          |

| E14 | RAM_DATA_CHK(6) | Вход/выход       | GPIO_C(14)         |

|     |                 | Микросхема интеа | еральная 5023BC016 |

Инв. № дубл.

Взам. инв. №

Подп. и дата

| Продолжение      | таблииы   | 1.2.1 |

|------------------|-----------|-------|

| 11poodsidicerric | masiniqui | 1.2.1 |

RAM\_DATA\_CHK(5)

$MKPD4_RX_B$

E15

F1

Инв. № дубл.

Взам. инв. №

Подп. и дата

Инв. Nº подл.

|     | 1,111 2111_2    | Влод выпод   | 3113_3(1)  |

|-----|-----------------|--------------|------------|

| F2  | MKPD4_nRX_A     | Вход/выход   | GPIO_F(13) |

| F3  | MKPD4_RX_A      | Вход/выход   | GPIO_F(12) |

| F13 | RAM_DATA_CHK(4) | Вход/выход   | GPIO_C(12) |

| F14 | RAM_DATA_CHK(3) | Вход/выход   | GPIO_C(11) |

| F15 | RAM_DATA_CHK(1) | Вход/выход   | GPIO_C(9)  |

| G1  | MKPD4_nRX_B     | Вход/выход   | GPIO_G(2)  |

| G2  | MKPD4_nTX_A     | Вход/выход   | GPIO_F(15) |

| G3  | MKPD4_TXEN_A    | Вход/выход   | GPIO_G(0)  |

| G13 | VCC2            | Питание UCC2 | Питание    |

| G14 | RAM_DATA_CHK(2) | Вход/выход   | GPIO_C(10) |

| G15 | RAM_DATA_CHK(0) | Вход/выход   | GPIO_C(8)  |

| H1  | GND             | Общий        | Питание    |

| H2  | TC_DIN(1)       | Вход/выход   | GPIO_H(2)  |

| Н3  | VCC1            | Питание UCC1 | Питание    |

| H13 | VCC1            | Питание UCC1 | Питание    |

| H14 | RAM_DATA(15)    | Вход/выход   | GPIO_C(7)  |

| H15 | GND             | Общий        | Питание    |

| J1  | TC_DIN(2)       | Вход/выход   | GPIO_H(3)  |

| J2  | SW_SIN(0)       | Вход/выход   | GPIO_G(4)  |

| J3  | VCC2            | Питание UCC2 | Питание    |

| J13 | RAM_DATA(12)    | Вход/выход   | GPIO_C(4)  |

| J14 | RAM_DATA(11)    | Вход/выход   | GPIO_C(3)  |

| J15 | RAM_DATA(14)    | Вход/выход   | GPIO_C(6)  |

| K1  | MKPD4_TXEN_B    | Вход/выход   | GPIO_G(3)  |

| K2  | SW_DIN(0)       | Вход/выход   | GPIO_G(5)  |

| K3  | SW_SOUT(0)      | Вход/выход   | GPIO_G(6)  |

| K13 | RAM_DATA(8)     | Вход/выход   | GPIO_C(0)  |

3

Вход/выход

Вход/выход

4

GPIO\_C(13)

$GPIO\_G(1)$

| 1   | 2             | 3            | 4                                 |

|-----|---------------|--------------|-----------------------------------|

| K14 | RAM_DATA(9)   | Вход/выход   | GPIO_C(1)                         |

| K15 | RAM_DATA(13)  | Вход/выход   | GPIO_C(5)                         |

| L1  | SW_DOUT(0)    | Вход/выход   | GPIO_G(7)                         |

| L2  | SW_SIN(1)     | Вход/выход   | GPIO_G(8)                         |

| L3  | TM_CLKI       | Вход/выход   | GPIO_G(12)                        |

| L13 | RAM_DATA(4)   | Вход/выход   | GPIO_B(12)                        |

| L14 | RAM_DATA(6)   | Вход/выход   | GPIO_B(14)                        |

| L15 | RAM_DATA(10)  | Вход/выход   | GPIO_C(2)                         |

| M1  | SW_DIN(1)     | Вход/выход   | GPIO_G(9)                         |

| M2  | SW_DOUT(1)    | Вход/выход   | GPIO_G(11)                        |

| M3  | TC_CLKI       | Вход/выход   | GPIO_G(15)                        |

| M13 | VCC2          | Питание UCC2 | Питание                           |

| M14 | RAM_DATA(3)   | Вход/выход   | GPIO_B(11)                        |

| M15 | RAM_DATA(7)   | Вход/выход   | GPIO_B(15)                        |

| N1  | SW_SOUT(1)    | Вход/выход   | GPIO_G(10)                        |

| N2  | TM_DOUT_VALID | Вход/выход   | GPIO_G(13)                        |

| N3  | TC_ACT        | Вход/выход   | GPIO_H(0)                         |

| N4  | VCC2          | Питание UCC2 | Питание                           |

| N5  | JTAG_TRST     | Вход         | Сброс контроллера интерфейса JTAG |

| N6  | JTAG_TDO      | Выход        | Выход данных интерфейса<br>JTAG   |

| N7  | RAM_ADDR(1)   | Вход/выход   | GPIO_A(1)                         |

| N8  | VCC1          | Питание UCC1 | Питание                           |

Питание UCC2

Вход/выход

Вход/выход

Вход/выход

Питание UCC1

Вход

Подп. и дата Взам. инв. № Инв. № дубл. Подп. и

1нв. № подл.

N9

N10

N11

N12

N13

N14

| Изм | Лист | № докум. | Подп. | Дата |

|-----|------|----------|-------|------|

VCC2

VCC1

RAM\_ADDR(9)

RAM\_ADDR(15)

JTAG\_Select

$RAM_DATA(0)$

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 от 01.09.2017 г.

Питание

$GPIO_A(9)$

GPIO\_A(15)

GPIO\_B(8)

Питание

Выбор контроллера

интерфейса JTAG

| $\boldsymbol{\Pi}$ | _           | 1 2  | 1 |

|--------------------|-------------|------|---|

| Продолжение        | $man\pi mu$ | 1 /  | 1 |

| 11poodsisicenine   | тиолицы     | 1.4. | 1 |

RAM\_DATA(5)

TM\_DOUT

N15

P1

| P2               | TC_DIN(0)    | Вход/выход   | GPIO_H(1)                                         |  |

|------------------|--------------|--------------|---------------------------------------------------|--|

| P3               | VCC1         | Питание UCC1 | Питание                                           |  |

| P4               | RST          | Вход         | Сброс микросхемы. Активный уровень – «0»          |  |

| P5               | JTAG_TMS     | Вход         | Выбор режима интерфейса<br>JTAG                   |  |

| P6               | ExEDAC_En    | Вход         | Включение блока исправления ошибок внешней памяти |  |

| P7               | RAM_ADDR(0)  | Вход/выход   | GPIO_A(0)                                         |  |

| P8               | RAM_ADDR(4)  | Вход/выход   | GPIO_A(4)                                         |  |

| P9               | RAM_ADDR(7)  | Вход/выход   | GPIO_A(7)                                         |  |

| P10              | RAM_ADDR(8)  | Вход/выход   | GPIO_A(8)                                         |  |

| P11              | RAM_ADDR(11) | Вход/выход   | GPIO_A(11)                                        |  |

| P12              | RAM_ADDR(14) | Вход/выход   | GPIO_A(14)                                        |  |

| P13              | RAM_ADDR(16) | Вход/выход   | GPIO_B(0)                                         |  |

| P14              | RAM_DATA(1)  | Вход/выход   | GPIO_B(9)                                         |  |

| P15              | RAM_DATA(2)  | Вход/выход   | GPIO_B(10)                                        |  |

| Q1               | GND          | Общий        | Питание                                           |  |

| Q2               | CLK          | Вход         | Тактовый сигнал цифровой части микросхемы         |  |

| Q3               | JTAG_TCK     | Вход         | Тактовый сигнал интерфейса<br>JTAG                |  |

| Q4               | JTAG_TDI     | Вход         | Вход данных интерфейса<br>JTAG                    |  |

| Q5               | Ex8_16bit    | Вход         | Выбор режима работы интерфейса внешней памяти     |  |

| Q6               | RAM_ADDR(2)  | Вход/выход   | GPIO_A(2)                                         |  |

| Q7               | RAM_ADDR(3)  | Вход/выход   | GPIO_A(3)                                         |  |

| Q8               | GND          | Общий        | Питание                                           |  |

| Q9               | RAM_ADDR(5)  | Вход/выход   | GPIO_A(5)                                         |  |

| Q10              | RAM_ADDR(6)  | Вход/выход   | GPIO_A(6)                                         |  |

| Q11              | RAM_ADDR(10) | Вход/выход   | GPIO_A(10)                                        |  |

| Q12 RAM_ADDR(12) |              | Вход/выход   | GPIO_A(12)                                        |  |

3

GPIO\_B(13)

GPIO\_G(14)

Вход/выход

Вход/выход

№ докум.

Лист

Подп.

Дата

Инв. № дубл.

Взам. инв. №

Продолжение таблицы 1.2.1

| 1   | 2            | 3          | 4          |

|-----|--------------|------------|------------|

| Q13 | RAM_ADDR(13) | Вход/выход | GPIO_A(13) |

| Q14 | RAM_ADDR(17) | Вход/выход | GPIO_B(1)  |

| Q15 | GND          | Общий      | Питание    |

Выводы могут использоваться как в качестве интерфейсных сигналов, так и в режиме General Purpose input-output (GPIO). В режиме GPIO выводы разбиты на порты по 16 выводов в каждом. Управление каждым портом осуществляется с помощью контроллера портов ввода-вывода (п. 3.7).

Каждый вывод может поддерживать от одного до трех различных интерфейсных сигналов в режиме включенной альтернативной функции. Выбор используемой альтернативной функции осуществляется путем записи в регистры ALT\_FUNCTION\_CTRL в блоке регистров общего назначения. В таблице 1.2.2 приведено соответствие интерфейсных сигналов для различных альтернативных функций, и портов ввода-вывода, описанных в таблице 1.2.1.

Таблица 1.2.2 — Соответствие интерфейсных сигналов и портов ввода-вывода

| Номер порта<br>ввода-вывода | ALT_FUNC_1   | ALT_FUNC_2 | ALT_FUNC_3 | PAD |

|-----------------------------|--------------|------------|------------|-----|

| 1                           | 2            | 3          | 4          | 5   |

| A[0]                        | RAM_ADDR[0]  |            |            | P7  |

| A[1]                        | RAM_ADDR[1]  |            |            | N7  |

| A[2]                        | RAM_ADDR[2]  |            |            | Q6  |

| A[3]                        | RAM_ADDR[3]  |            |            | Q7  |

| A[4]                        | RAM_ADDR[4]  |            |            | P8  |

| A[5]                        | RAM_ADDR[5]  |            |            | Q9  |

| A[6]                        | RAM_ADDR[6]  |            |            | Q10 |

| A[7]                        | RAM_ADDR[7]  |            |            | P9  |

| A[8]                        | RAM_ADDR[8]  |            |            | P10 |

| A[9]                        | RAM_ADDR[9]  |            |            | N10 |

| A[10]                       | RAM_ADDR[10] |            |            | Q11 |

| A[11]                       | RAM_ADDR[11] |            |            | P11 |

| A[12]                       | RAM_ADDR[12] |            |            | Q12 |

| A[13]                       | RAM_ADDR[13] |            |            | Q13 |

Изм Лист № докум. Подп. Дата

Инв. № дубл.

Взам. инв. №

Подп. и дата

1нв. Nº подл.

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 om 01.09.2017 г.

| 1     | 2                | 3                    | 4         | + |

|-------|------------------|----------------------|-----------|---|

| A[14] | RAM_ADDR[14]     |                      |           | I |

| A[15] | RAM_ADDR[15]     |                      |           | N |

| B[0]  | RAM_ADDR[16]     |                      |           | I |

| B[1]  | RAM_ADDR[17]     |                      |           | ( |

| B[8]  | RAM_DATA[0]      |                      |           | N |

| B[9]  | RAM_DATA[1]      |                      |           | I |

| B[10] | RAM_DATA[2]      |                      |           | I |

| B[11] | RAM_DATA[3]      |                      |           | N |

| B[12] | RAM_DATA[4]      |                      |           | I |

| B[13] | RAM_DATA[5]      |                      |           | N |

| B[14] | RAM_DATA[6]      |                      |           | I |

| B[15] | RAM_DATA[7]      |                      |           | N |

| C[0]  | RAM_DATA[8]      | MKPD3_RX_A           | SPI1_SS   | ŀ |

| C[1]  | RAM_DATA[9]      | MKPD3_nRX_A          | SPI1_SCK  | ŀ |

| C[2]  | RAM_DATA[10]     | MKPD3_TX_A           | SPI1_MISO |   |

| C[3]  | RAM_DATA[11]     | MKPD3_nTX_A          | SPI1_MOSI |   |

| C[4]  | RAM_DATA[12]     | MKPD3_TXEN_A         | SPI2_SS   |   |

| C[5]  | RAM_DATA[13]     | MKPD3_RX_B           | SPI2_SCK  | ŀ |

| C[6]  | RAM_DATA[14]     | MKPD3_nRX_B          | SPI2_MISO |   |

| C[7]  | RAM_DATA[15]     | MKPD3_TXEN_B         | SPI2_MOSI | F |

| C[8]  | RAM_DATA_CHK[0]  |                      |           | ( |

| C[9]  | RAM_DATA_ CHK[1] |                      |           | I |

| C[10] | RAM_DATA_ CHK[2] |                      |           | ( |

| C[11] | RAM_DATA_ CHK[3] |                      |           | I |

| C[12] | RAM_DATA_ CHK[4] |                      |           | I |

| C[13] | RAM_DATA_ CHK[5] |                      | UART1_TxD | I |

| C[14] | RAM_DATA_ CHK[6] |                      | UART1_RxD | I |

| C[15] | RAM_DATA_ CHK[7] |                      | UART2_TxD | I |

| D[0]  | RAM_DATA_ CHK[8] |                      | UART2_RxD | ( |

|       |                  | Микросхема интеграль | 500000010 |   |

Взам. инв. № Инв. № дубл.

Подп. и дата

| 1                 | 2                | 3                    | 4             | 5  |

|-------------------|------------------|----------------------|---------------|----|

| D[1]              | RAM_DATA_ CHK[9] |                      |               | D1 |

| D[2]              | RAM_Wen          |                      |               | E1 |

| D[4]              | RAM_Oen          |                      |               | C1 |

| D[5]              | RAM_LBn          |                      |               | B1 |

| D[6]              | RAM_Ubn          |                      |               | Di |

| D[7]              | SPI1_SS          | UART1_TxD            |               | C  |

| D[8]              | SPI1_SCK         | UART1_RxD            |               | B  |

| D[9]              | SPI1_MISO        | UART2_TxD            |               | A. |

| D[10]             | SPI1_MOSI        | UART2_RxD            |               | B  |

| D[11]             | SPI2_SS          | SW1_SIN              |               | C  |

| D[12]             | SPI2_SCK         | SW1_DIN              |               | A  |

| D[13]             | SPI2_MISO        | SW1_SOUT             |               | B  |

| D[14]             | SPI2_MOSI        | SW1_DOUT             |               | A  |

| D[15]             | UART1_TxD        | SW2_SIN              |               | A  |

| E[0]              | UART1_RxD        | SW2_DIN              |               | В  |

| E[1]              | UART2_TX         | SW2_SOUT             |               | С  |

| E[2]              | UART2_RX         | SW2_DOUT             |               | С  |

| E[3]              | RAM_Cen0         |                      |               | Е  |

| E[4]              | MKPD1_RX_A       | SPI1_SS              |               | C  |

| E[5]              | MKPD1_nRX_A      | SPI1_SCK             |               | В  |

| E[6]              | MKPD1_TX_A       | SPI1_MISO            |               | A  |

| E[7]              | MKPD1_nTX_A      | SPI1_MOSI            |               | В  |

| E[8]              | MKPD1_TXEN_A     | SPI2_SS              |               | С  |

| E[9]              | MKPD1_RX_B       | SPI2_SCK             |               | A  |

| E[10]             | MKPD1_nRX_B      | SPI2_MISO            |               | A  |

| E[11]             | MKPD1_TXEN_B     | SPI2_MOSI            |               | A  |

| E[12]             | MKPD2_RX_A       |                      | I2C_SCL       | В  |

| E[13] MKPD2_nRX_A |                  |                      | I2C_SDA       | В  |

| E[14]             | MKPD2_TX_A       | CAN1_TX              |               | C  |

| <u> </u>          |                  | Ликросхема интеграль | иза 5023RC016 | b  |

Взам. инв. № Инв. № дубл.

Подп. и дата

| 1     | 2            | 3                                      | 4             |   |

|-------|--------------|----------------------------------------|---------------|---|

| E[15] | MKPD2_nTX_A  | CAN1_RX                                |               | A |

| F[0]  | MKPD2_TXEN_A | CAN2_TX                                |               | I |

| F[1]  | MKPD2_RX_B   | CAN2_RX                                |               | A |

| F[2]  | MKPD2_nRX_B  | UART3_TxD                              |               | A |

| F[3]  | MKPD2_TXEN_B | UART3_RxD                              |               | I |

| F[4]  | MKPD3_RX_A   |                                        | UART5_TxD     | 1 |

| F[5]  | MKPD3_nRX_A  |                                        | UART5_RxD     | ( |

| F[6]  | MKPD3_TX_A   |                                        | UART6_TxD     | ( |

| F[7]  | MKPD3_nTX_A  |                                        | SW1_SIN       | I |

| F[8]  | MKPD3_TXEN_A |                                        | SW1_DIN       | I |

| F[9]  | MKPD3_RX_B   |                                        | SW1_SOUT      | I |

| F[10] | MKPD3_nRX_B  |                                        | SW1_DOUT      | I |

| F[11] | MKPD3_TXEN_B | RAM_ADDR[23]                           |               | I |

| F[12] | MKPD4_RX_A   | RAM_Cen1                               |               | ] |

| F[13] | MKPD4_nRX_A  | RAM_Cen2                               |               | ] |

| F[14] | MKPD4_TX_A   | RAM_Cen3                               |               | ] |

| F[15] | MKPD4_nTX_A  | RAM_ADDR[18]                           |               |   |

| G[0]  | MKPD4_TXEN_A | RAM_ADDR[19]                           |               | ( |

| G[1]  | MKPD4_RX_B   | RAM_ADDR[20]                           |               | ] |

| G[2]  | MKPD4_nRX_B  | RAM_ADDR[21]                           |               | ( |

| G[3]  | MKPD4_TXEN_B | RAM_ADDR[22]                           |               | I |

| G[4]  | SW1_SIN      | MKPD4_RX_A                             |               |   |

| G[5]  | SW1_DIN      | MKPD4_nRX_A                            |               | I |

| G[6]  | SW1_SOUT     | MKPD4_TX_A                             |               | I |

| G[7]  | SW1_DOUT     | MKPD4_nTX_A                            |               | I |

| G[8]  | SW2_SIN      | MKPD4_TXEN_A                           |               | 1 |

| G[9]  | SW2_DIN      | MKPD4_RX_B                             |               | N |

| G[10] | SW2_SOUT     | MKPD4_nRX_B                            |               | 1 |

| G[11] | SW2_DOUT     | MKPD4_TXEN_B                           |               | N |

|       |              | Микросхема интегральн                  | ная 5023BC016 |   |

|       |              | Техническое опи<br>Версия 2.04 om 01.0 |               |   |

Взам. инв. № Инв. № дубл.

Подп. и дата

инв. № дубл.

Взам. инв. №

Подп. и дата

| 1     | 2             | 3 | 4         | 5  |

|-------|---------------|---|-----------|----|

| G[12] | TM_CLKI       |   | CAN1_TX   | L3 |

| G[13] | TM_DOUT_VALID |   | CAN1_RX   | N2 |

| G[14] | TM_DOUT       |   | CAN2_TX   | P1 |

| G[15] | TC_CLKI       |   | CAN2_RX   | M3 |

| H[0]  | TC_ACT        |   | UART3_TxD | N3 |

| H[1]  | TC_DIN[0]     |   | UART3_RxD | P2 |

| H[2]  | TC_DIN[1]     |   | UART4_TxD | H2 |

| H[3]  | TC_DIN[2]     |   | UART4_RxD | J1 |

| H[4]  | SW_CLK        |   | UART6_RxD | В8 |

#### 1.3 Электрические параметры микросхемы

Электрические параметры СБИС СРU при приёмке и поставке должны соответствовать нормам, приведённым в таблице 1.3.1.

Электрические параметры микросхем в процессе и после воздействия специальных факторов (ВСФ) должны соответствовать нормам, приведённым в таблице 1.3.1 для крайних значений рабочей температуры среды.

Значения предельно-допустимых и предельных режимов эксплуатации в диапазоне рабочих температур среды должны соответствовать нормам, приведённым в таблице 1.3.2.

Таблица 1.3.1 — Электрические параметры СБИС СРU при приёмке и поставке

| Полимоморомую моромогра                                                                              | Буквенное       | Норма параметра |          |          |          |                          |  |

|------------------------------------------------------------------------------------------------------|-----------------|-----------------|----------|----------|----------|--------------------------|--|

| Наименование параметра, единица измерения, режим                                                     | обозначен<br>ие | До В            | СФ       | Во время |          | Температура<br>среды, °С |  |

| измерения                                                                                            | параметра       | не менее        | не более | не менее | не более |                          |  |

| 1                                                                                                    | 2               | 3               | 4        | 5        | 6        | 7                        |  |

| 1 Выходное напряжение низкого уровня буферов                                                         | II              |                 | 0,4      |          | 0,4      | 25 ± 10                  |  |

| ввода-вывода, B, при $U_{CC1}=3.0~\mathrm{B};$ $U_{CC2}=1,62~\mathrm{B},~I_{OL}\leq 2.0~\mathrm{mA}$ | $ m U_{OL}$     | _               | 0,5      | _        | 0,5      | от – 60 до + 85          |  |

|    |        |          |       |      | Микросхема интегральная 5023ВС016 | Лист |

|----|--------|----------|-------|------|-----------------------------------|------|

|    |        |          |       |      | Техническое описание              |      |

| Из | и Лист | № докум. | Подп. | Дата | Версия 2.04 от 01.09.2017 г.      | 19   |

Копировал

Формат А4

| 1                                                                                                                                | 2                 | 3                             | 4                     | 5                             | 6                     | 7            |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------|-----------------------|-------------------------------|-----------------------|--------------|

| 2 Выходное напряжение высокого уровня буферов ввода-вывода, В,                                                                   | U <sub>ОН</sub>   | 2,7                           | _                     | 2,0                           | _                     | 25 ± 10      |

| при $U_{CC1} = 3.0 \text{ B};$ $U_{CC2} = 1.62 \text{ B}, I_{OH} \le -0.3 \text{ мA}$                                            | - 011             | 2,3                           |                       | 1,8                           |                       | от – 60 до + |

| 3 Ток потребления в                                                                                                              | $I_{CC1}$         |                               | 150                   | _                             | 220                   | 25 ± 10      |

| статическом режиме, мА,                                                                                                          | ICCI              | _                             | 250                   | _                             | 300                   | от – 60 до + |

| при U <sub>CC1</sub> = 3,6 B;<br>U <sub>CC2</sub> = 1,98 B                                                                       | $I_{\rm CC2}$     |                               | 65                    | _                             | 220                   | $25 \pm 10$  |

| O(C2 – 1,76 B                                                                                                                    | 1002              |                               | 70                    |                               | 300                   | от – 60 до + |

| 4 Ток утечки низкого и высокого уровня на входе, мкА, Входы «pulldown» (К3, N1) Входы «pullup» (L1, M2)                          | ${ m I}_{ m ILL}$ | - 15<br>- 200<br>- 55<br>- 15 | 200<br>15<br>55<br>15 | - 15<br>- 200<br>- 55<br>- 15 | 200<br>15<br>55<br>15 | 25 ± 10      |

| Вход X2/CLKIN (Q2)<br>Все остальные входы<br>при $U_{CC1} = 3,6$ B;<br>$U_{CC2} = 1,98$ B, $U_{IL} = 0$ В<br>( $U_{IH} = 3,6$ В) | ${ m I_{ILH}}$    | -25<br>-300<br>-75<br>-25     | 300<br>25<br>75<br>25 | - 25<br>- 300<br>- 75<br>- 25 | 300<br>25<br>75<br>25 | от – 60 до + |

| 5 Выходной ток низкого и высокого уровня буфера с третьим состоянием в состоянии «Выключено»,                                    | I <sub>OZL</sub>  | - 15                          | 15                    | - 15                          | 15                    | 25 ± 10      |

| мкА, при $U_{CC1} = 3,6 B$ ; $U_{CC2} = 1,98 B$ $U_{OL} = 0 B (U_{OH} = 3,6 B)$                                                  | $I_{\rm OZH}$     | - 25                          | 25                    | - 25                          | 25                    | от – 60 до + |

| 6 Динамический ток потребления ядра, мА, при $U_{CC1} = 3,6 B$ ;                                                                 | I <sub>OCC</sub>  |                               | 300                   | _                             | 450                   | 25 ± 10      |

| При ССС1 3,0 В, $U_{CC2} = 1,98 B$ $fc = 40 M\Gamma$ ц и $C_L \le 20 \pi \Phi^{1)}$                                              | 1000              | _                             | 350                   | _                             | 550                   | от – 60 до + |

| 7 Функциональный контроль (ФК) при $U_{CC1} = 2,97 \ B;$ $U_{CC2} = 1,62 \ B,$                                                   | ФК                |                               |                       |                               |                       | 25 ± 10      |

| при $U_{CC1}$ = 3,63 B; $U_{CC2}$ = 1,98 B, $f_C$ = 50 МГц и $C_L$ = 20 п $\Phi^{1)}$                                            |                   |                               |                       |                               |                       | от – 60 до + |

| 8 Входная емкость, пФ                                                                                                            | Cı                |                               | 12                    |                               | 12                    | 25 ± 10      |

| 9 Выходная емкость, пФ                                                                                                           | Co                |                               | 12                    |                               | 12                    | ± 10         |

| 10 Емкость входа/выхода, пФ                                                                                                      | C <sub>I/O</sub>  |                               | 14                    |                               | 14                    | 25 ± 10      |

| • • • • • • • • • • • • • • • • • • • •                                                                                          |                   |                               |                       |                               |                       | <u> </u>     |

Инв. № дубл.

Взам. инв. №

Подп. и дата

Инв. № подл.

Лист

№ докум.

Подп.

Дата

Техническое описание

Версия 2.04 от 01.09.2017 г.

20

Примечание — В процессе и непосредственно после воздействия специального фактора 7.И с характеристикой 7.И6 требования к значениям электрических параметров не предъявляют на время потери работоспособности, указанной в пункте 2.6.1 АЕЯР.431290.994 ТУ.

Таблица 1.3.2 — Предельно-допустимые и предельные режимы эксплуатации микросхемы

| Наименование<br>параметра режима,                                             | Буквенное<br>обозначение          |          | -допустимый<br>жим                 | Предельный режим |                                    |

|-------------------------------------------------------------------------------|-----------------------------------|----------|------------------------------------|------------------|------------------------------------|

| единица измерения                                                             | параметра                         | не менее | не более                           | не менее         | не более                           |

| Напряжение питания<br>буферов ввода-вывода, В                                 | U <sub>CC1</sub>                  | 3,0      | 3,6                                | - 0,3            | 4,51)                              |

| Напряжение питания ядра, В                                                    | U <sub>CC2</sub>                  | 1,62     | 1,98                               | -0,2             | $2,5^{1)}$                         |

| Входное напряжение низкого уровня на входах, В                                | $ m U_{IL}$                       | 0        | 0,8                                | -0,3             | _                                  |

| Входное напряжение высокого уровня на входах, В                               | $ m U_{IH}$                       | 2,0      | U <sub>CC1</sub>                   | _                | U <sub>CC1</sub> + 0,3             |

| Выходное напряжение на выходе с третьим состоянием в состоянии «Выключено», В | Uoz                               | 0        | U <sub>CC1</sub>                   | - 0,3            | U <sub>CC1</sub> + 0,3             |

| Выходной ток низкого уровня, мА                                               | $I_{OL}$                          | _        | 1,5                                | _                | 2,0                                |

| Выходной ток высокого уровня, мА                                              | $I_{OH}$                          |          | -0,3                               |                  | -0,5                               |

| Частота следования импульсов тактовых сигналов, МГц                           | $f_{\mathrm{C}}$                  | 5        | 50 <sup>4)</sup>                   | _                | _                                  |

| Время нарастания и спада входных сигналов, нс                                 | t <sub>LH</sub> и t <sub>HL</sub> | _        | 0,05T <sub>CLK</sub> <sup>2)</sup> | _                | 0,05T <sub>CLK</sub> <sup>2)</sup> |

| Ёмкость нагрузки, пФ                                                          | $C_{L}$                           | _        | 203)                               | _                | 403)                               |

<sup>1)</sup> С учётом всех видов помех.

Инв. № дубл.

Взам. инв. №

Подп. и дата

нв. № подл.

Примечание – Время работы микросхем в одном из предельных режимов по току или напряжению не должно превышать 5 с.

Изм Лист № докум. Подп. Дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 от 01.09.2017 г.

$<sup>^{2)}</sup>$  При переключении входных сигналов.

<sup>3)</sup> С учётом всех паразитных емкостей.

<sup>&</sup>lt;sup>4)</sup> С приёмкой «5».

Таблица 1.3.3 — Средний ток потребления ядра в основных режимах работы микросхемы (напряжение питания  $U_{cc2}=1{,}98~B,~T=25{,}0~^{\circ}C,~f_c=50~M\Gamma$ ц и  $f_c=80~M\Gamma$ ц)

| Downers no Soms                                     | Ток потребления, мА |             |  |  |

|-----------------------------------------------------|---------------------|-------------|--|--|

| Режимы работы                                       | fc = 50 МГц         | fc = 80 МГц |  |  |

| Работает ПдТМИ и UART1                              | 481                 | 665         |  |  |

| Работает ПрТКИ и UART1                              | 301                 | 403         |  |  |

| Работает вычислитель с плавающей запятой и UART1    | 236                 | 302         |  |  |

| Работают 4 контроллера по ГОСТ Р 52070 и UART1      | 315                 | 424         |  |  |

| Работают 2 контроллера интерфейса SpaceWire и UART1 | 321                 | 440         |  |  |

| Работают 2 контроллера SPI и UART1                  | 220                 | 284         |  |  |

| Работают 2 контроллера UART                         | 217                 | 285         |  |  |

СБИС CPU стойкая к воздействию специальных факторов, приведённых в таблице 1.3.4.

Таблица 1.3.4 — Стойкость к воздействию специальных факторов

| Характеристики специальных факторов | Значения характеристик специальных факторов |

|-------------------------------------|---------------------------------------------|

| 7.И1                                | 4Ус                                         |

| 7.И6                                | 4Ус                                         |

| 7.И7                                | 4Ус                                         |

| 7.И8                                | 0,02 · 1Ус                                  |

| 7.C1                                | 4Ус                                         |

| 7.C4                                | 4Ус                                         |

| 7.K1                                | $1K^{1)}(2K^{2)};$                          |

| 7.K4                                | 1К                                          |

| 7.K12                               | 60 <sup>3)</sup> МэВ · см²/мг               |

<sup>2)</sup> При независимом воздействии факторов 7.К1 и 7.К4.

| Изм | Лист | № докум. | Подп. | Дата |

|-----|------|----------|-------|------|

Инв. Nº дубл.

Взам. инв. №

Подп. и дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 om 01.09.2017 г.

<sup>3)</sup> По катастрофическим отказам и тиристорному эффекту.

## 2 Общая характеристика СБИС СРИ

Системная шина микросхемы разделена на высокоскоростную шину Advanced Microcontroller Bus Architecture (AMBA) High-performance Bus (AHB) и низкоскоростную AMBA Advanced Peripheral Bus (APB).

Шина АМВА АНВ предназначена для связи высокоскоростных устройств:

- ядра процессора;

- оперативной памяти;

- контроллера прямого доступа к памяти (ПДП);

- интерфейсов SpaceWire;

- блоков мультиплексного канала передачи данных (МКПД);

- блоков ПдТМИ и ПрТКИ.

Шина AMBA APB предназначена для подключения низкоскоростных устройств:

- контроллеров последовательных портов;

- интерфейсов управления ПдТМИ и ПрТКИ и ПДП;

- таймеров;

- контроллеров интерфейсов CAN;

- $--I^2C$ .

Инв. № дубл.

Взам. инв. №

Подп. и дата

нв. № подл.

Функционирование шины обеспечивается блоками:

— AHB BusMUX — мультиплексор ведущих и ведомых устройств шины AMBA AHB. Данный блок выполняет арбитраж доступа ведущих устройств на шине к ведомым, а также передачу ответов в обратную сторону, обеспечивая доступ к шине всем устройствам с одинаковым приоритетом;

- АНВ-АРВ МОСТ выполняет передачу данных между шинами АНВ и АРВ;

- APB SLAVE MUX мультиплексор ведомых устройств шины AMBA APB. Данный блок выполняет передачу сигналов управления на ведомые устройства шины, а также передачу ответов в обратную сторону.

Блок ФТС выполняет формирования сетки тактовых частот, необходимых для работы схемы, а также пересинхронизацию сигнала сброса.

Изм Лист № докум. Подп. Дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 om 01.09.2017 г. Лист

23

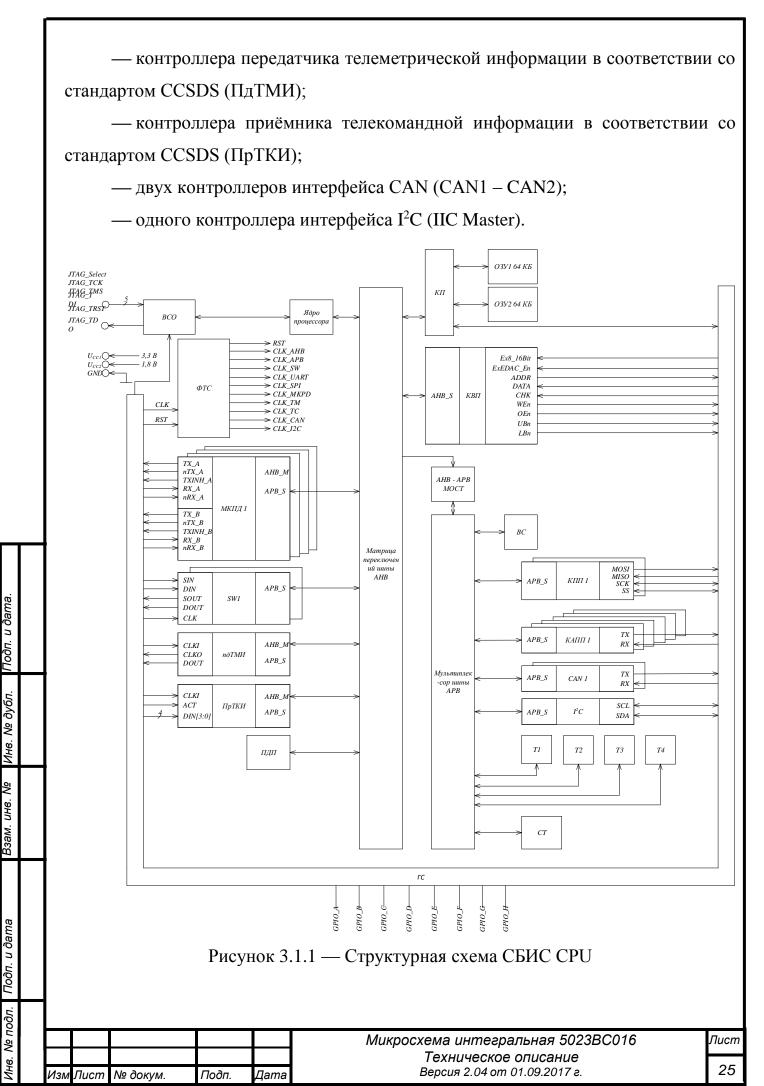

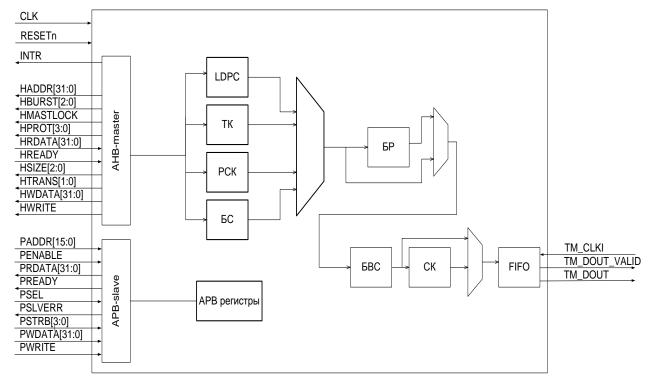

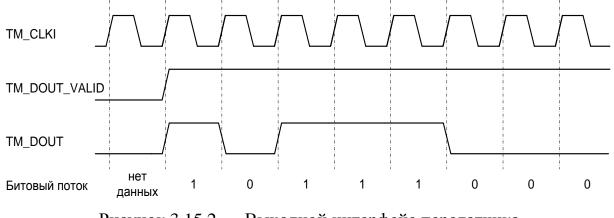

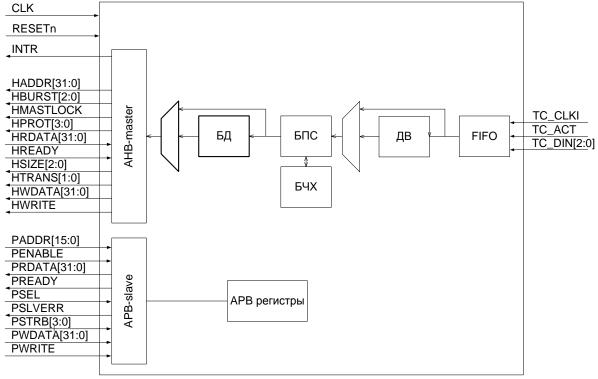

# 3.1 Структурная организация микросхемы Структурная схема СБИС СРU приведена на рисунке 3.1.1. СБИС СРU состоит из следующих функциональных блоков: — 32-разрядного процессорного ядра (CPU CORE); — мультиплексора устройств шины AMBA AHB (матрица переключений шины АНВ); — моста между шинами AMBA AHB и AMBA APB (AHB-APB MOCT); — мультиплексора ведомых устройств шины AMBA APB (APBSLAVEMUX); — блока формирования тактовых сигналов и сигналов сброса (ФТС); контроллера прямого доступа к памяти (ПДП); — четырех резервированных контроллеров последовательного интерфейса по ГОСТ Р 52070 (МКПД1 – МКПД4); — двух контроллеров интерфейса SpaceWire со скоростью передачи данных до 100 Мбит/c (SW1 – SW2);— внутрикристальной схемы отладки с интерфейсом JTAG (IEEE 1149.1) (BCO); блока граничного сканирования (ГС); — встроенного оперативного запоминающего устройства, состоящего из двух блоков по 64 кБ (O3У1 – O3У2); — контроллера встроенного ОЗУ с блоком обнаружения и исправления ошибок; — контроллера внешней статической памяти со встроенным блоком обнаружения и исправления ошибок (КВП); — шести асинхронных последовательных портов UART (КАПП1 – КАПП6); двух последовательных портов SPI (КПП1 – КПП2); специализированного вычислителя с плавающей запятой (BC); — четырех таймеров общего назначения (T1 – T4); сторожевого таймера (СТ); Микросхема интегральная 5023ВС016 Лист

3 Описание микросхемы

Инв. № дубл.

Взам. инв. №

Подп. и дата

нв. № подл.

Лист

№ докум.

Подп.

*Д*ата

24

Техническое описание

Версия 2.04 от 01.09.2017 г.

#### JTAG\_SELECT:

- 0 выводы JTAG перенаправлены к программатору и отладчику ARM процессора;

- 1 выводы JTAG перенаправлены к Boundary Scan контроллеру.

Ex8\_16bit: режим работы внешней памяти по Chip Select 1:

- 0 8-битный режим;

- 1 16-битный режим.

ExEDAC\_En: включение режима исправления единичных и обнаружения неисправимых ошибок во внешней памяти по Chip Select 1.

В 8-битном режиме используются выводы RAM\_DATA\_CHK [4:0], в 16-битном режиме — RAM\_DATA\_CHK [9:0].

#### 3.1.2 Инициализация работы микросхемы

Перед началом работы микросхемы должны быть настроены внешние выводы контроллера внешней памяти ExEDAC\_En и Ex8\_16bit. ExEDAC\_En управляет включением/выключением блока обнаружения и исправления ошибок (EDAC) контроллера внешней памяти по Chip Select 1.

Начальная загрузка происходит через Chip Select 1. В таблице 3.1.1 представлено соответствие Chip Select и выводов.

Таблица 3.1.1 — Соответствие Chip Select и выводов

Инв. № дубл.

Взам. инв. №

Подп. и дата

| CS            | Название<br>функции | Номер порта<br>ввыда-вывода | Номер<br>альтернативной<br>функции | Номер вывода |

|---------------|---------------------|-----------------------------|------------------------------------|--------------|

| Chip Select 1 | RAM_Cen0            | E[3]                        | ALT_FUNC_1                         | E2           |

| Chip Select 2 | RAM_Cen1            | F[12]                       | ALT_FUNC_2                         | F3           |

| Chip Select 3 | RAM_Cen2            | F[13]                       | ALT_FUNC_2                         | F2           |

| Chip Select 4 | RAM_Cen3            | F[14]                       | ALT_FUNC_2                         | E1           |

Если на вывод ExEDAC\_En подаётся уровень логической единицы, то EDAC включен. Если ExEDAC\_En подключен к земле, то EDAC выключен. Ex8\_16bit переключает режим 8/16 бит контроллера внешней памяти. При Ex8\_16bit равном

|     |      |          |       |      | Микросхема интегральная 5023ВС016 | Лист |

|-----|------|----------|-------|------|-----------------------------------|------|

|     |      |          |       |      | Техническое описание              |      |

| Изм | Лист | № докум. | Подп. | Дата | Версия 2.04 от 01.09.2017 г.      | 26   |

Копировал

Формат А4

После подачи питаний  $U_{CC1}$  и  $U_{CC2}$  микросхема должна быть сброшена внешним сигналом на выводе RST. Одновременно с сигналом сброса должен подаваться тактовый сигнал на вывод CLK. Минимальная длительность сигнала сброса должна быть не менее 2 периодов тактового сигнала. Активный уровень сигнала сброс — логический ноль.

Перед началом работы с периферийными модулями микросхемы необходимо включить тактовые сигналы этих модулей. Включение тактовых сигналов осуществляется в регистре общего назначения PWR\_CTRL\_CLK. Также должен быть снят сброс соответствующего модуля в регистре PWR CTRL RST.

#### 3.2 Распределение адресного пространства СБИС СРИ

Распределение адресного пространства микросхемы показано в таблице 3.2.1.

Таблица 3.2.1 — Структура адресного пространства

Инв. № дубл.

Взам. инв. №

Подп. и дата

нв. № подл.

№ докум.

Подп.

Дата

| Адрес                     | Описание                                                                                                                                           |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                         | 2                                                                                                                                                  |  |

| 0x0000_0000 - 0x00FF_FFFF | Алиасинг для областей: Внешняя память Chip Select 1-4, внутренняя память блок 1, внутренняя память блок 2. По сбросу: внешняя память Chip Select 1 |  |

| 0x0800_0000 - 0x08FF_FFFF | Внешняя память Chip Select 1                                                                                                                       |  |

| 0x0900_0000 - 0x09FF_FFFF | Внешняя память Chip Select 2                                                                                                                       |  |

| 0x0A00_0000 - 0x0AFF_FFFF | Внешняя память Chip Select 3                                                                                                                       |  |

| 0x0B00_0000 - 0x0BFF_FFFF | Внешняя память Chip Select 4                                                                                                                       |  |

| 0x2000_0000 - 0x2000_FFFF | Внутренняя память блок 1                                                                                                                           |  |

| 0x2001_0000 - 0x2001_FFFF | Внутренняя память блок 2                                                                                                                           |  |

| 0x8000_0000 - 0x8000_0FFF | GPIO_A                                                                                                                                             |  |

| 0x8001_0000 - 0x8001_0FFF | GPIO_B                                                                                                                                             |  |

| 0x8002_0000 - 0x8002_0FFF | GPIO_C                                                                                                                                             |  |

| 0x8003_0000 - 0x8003_0FFF | GPIO_D                                                                                                                                             |  |

| 0x8004_0000 - 0x8004_0FFF | GPIO_E                                                                                                                                             |  |

| 0x8005_0000 - 0x8005_0FFF | GPIO_F                                                                                                                                             |  |

| 0x8006_0000 - 0x8006_0FFF | GPIO_G                                                                                                                                             |  |

|                           | ·<br>·                                                                                                                                             |  |

Микросхема интегральная 5023BC016 Техническое описание

Версия 2.04 от 01.09.2017 г.

27

| l   | Продолжение таблицы 3.2    | 2.1                                                                         |     |  |  |  |

|-----|----------------------------|-----------------------------------------------------------------------------|-----|--|--|--|

|     | 1                          | 2                                                                           |     |  |  |  |

|     | 0x8007_0000 - 0x8007_0FFF  | GPIO_H                                                                      |     |  |  |  |

|     | 0x8008_0000 - 0x8008_0FFF  | GPIO_I                                                                      |     |  |  |  |

|     | 0xA000_0000 - 0xA000_FFFF  | Регистры общего назначения                                                  |     |  |  |  |

|     | 0xA001_0000 - 0xA001_0FFF  | DMA контроллер                                                              |     |  |  |  |

|     | 0xA002_0000 - 0xA002_0FFF  | SPI_1                                                                       |     |  |  |  |

|     | 0xA003_0000 - 0xA003_0FFF  | SPI_2                                                                       |     |  |  |  |

|     | 0xA004_0000 - 0xA004_0FFF  | UART_1                                                                      |     |  |  |  |

|     | 0xA005_0000 - 0xA005_0FFF  | UART_2                                                                      |     |  |  |  |

|     | 0xA006_0000 - 0xA006_0FFF  | UART_3                                                                      |     |  |  |  |

|     | 0xA007_0000 - 0xA007_0FFF  | UART_4                                                                      |     |  |  |  |

|     | 0xA008_0000 - 0xA008_0FFF  | WatchDog                                                                    |     |  |  |  |

|     | 0xA009_0000 - 0xA009_0FFF  | Timer 1                                                                     |     |  |  |  |

|     | 0xA00A_0000 - 0xA00A_FFFF  | SpaceWire_1                                                                 |     |  |  |  |

|     | 0xA00B_0000 - 0xA00B_FFFF  | SpaceWire_2                                                                 |     |  |  |  |

|     | 0xA00C_0000 - 0xA00C_FFFF  | МКПД_1                                                                      |     |  |  |  |

|     | 0xA00D_0000 - 0xA00D_FFFF  | МКПД _2                                                                     |     |  |  |  |

|     | 0xA00E_0000 - 0xA00E_FFFF  | МКПД_3                                                                      |     |  |  |  |

|     | 0xA00F_0000 - 0xA00F_FFFF  | МКПД _4                                                                     |     |  |  |  |

|     | 0xA010_0000 - 0xA010_FFFF  | Telemetry Encoder (TMTX)                                                    |     |  |  |  |

|     | 0xA011_0000 - 0xA011_FFFF  | TCRX                                                                        |     |  |  |  |

|     | 0xA012_0000 - 0xA012_FFFF  | Floating Point Unit (FPU)                                                   |     |  |  |  |

|     | 0xA013_0000 - 0xA013_FFFF  | Timer 2                                                                     |     |  |  |  |

|     | 0xA014_0000 - 0xA014_FFFF  | Timer 3                                                                     |     |  |  |  |

|     | 0xA015_0000 - 0xA015_FFFF  | Timer 4                                                                     |     |  |  |  |

|     | 0xA01B_0000 - 0xA01B_FFFF  | CAN 1                                                                       |     |  |  |  |

|     | 0xA01C_0000 - 0xA01C_FFFF  | CAN 2                                                                       |     |  |  |  |

|     | 0xA01D_0000 - 0xA01D_FFFF  | Мультиплексор прерываний                                                    |     |  |  |  |

|     | 0xA01E_0000 - 0xA01E_FFFF  | UART_5                                                                      |     |  |  |  |

|     | 0xA01F_0000 - 0xA01F_FFFF  | UART_6                                                                      |     |  |  |  |

|     | 0xA020_0000 - 0xA020_FFFF  | I <sup>2</sup> C                                                            |     |  |  |  |

|     | 0x6000_0000 - 0x6000_FFFF  | Тестовый доступ к памяти блок 1, данные                                     |     |  |  |  |

|     | 0x6010_0000 - 0x6010_FFFF  | Тестовый доступ к памяти блок 1, биты ECC (доступно 20 битмаска 0x1F1F1F1F) | г,  |  |  |  |

|     |                            |                                                                             |     |  |  |  |

|     |                            | Микросхема интегральная 5023BC016                                           | Лис |  |  |  |

| 131 | л Лист № докум. Подп. Дата | Техническое описание<br>Версия 2.04 от 01.09.2017 г.                        | 2   |  |  |  |

Инв. № дубл.

Взам. инв. №

Подп. и дата

Инв. Nº подл.

| 1                         | 2                                                              |

|---------------------------|----------------------------------------------------------------|

| 0x6100_0000 - 0x6100_3FFF | Тестовый доступ к памяти кэша way1 данные                      |

| 0x6110_0000 - 0x6110_3FFF | Тестовый доступ к памяти кэша way1 таг и crc (доступен 21 бит) |

| 0x6200_0000 - 0x6200_FFFF | Тестовый доступ к памяти блок 2, данные                        |

| 0x6210_0000 - 0x6210_FFFF | Тестовый доступ к памяти блок 2, биты ЕСС (доступно 20 бит)    |

#### 3.3 Вектора прерываний СБИС СРИ

Процессор имеет 32 вектора прерываний.

Управляющие регистры ссылаются на базовый адрес Мультиплексора прерываний — 0xA01D\_0000.

Каждому источнику прерывания соответствует свой управляющий регистр, с адресом, равным номеру источника прерываний, умноженному на 4.

Для ΤΟΓΟ чтобы подключить требуемый источник прерываний определенный вектор прерываний, нужно запрограммировать соответствующий (соответствует номеру источника прерывания) управляющий регистр мультиплексора прерываний. Также необходимо разрешить прерывания, вызвав NVIC En IRQ(vec), где vec — номер вектора прерываний.

Источники прерываний, которые подключены на один и тот же вектор прерываний, объединяются по «ИЛИ».

## 3.3.1 Регистры INTR MUX CTRL

Таблица 3.3.1 содержит описание регистра INTR MUX CTRL.

Таблица 3.3.1 — Описание регистра INTR\_MUX\_CTRL

| <b>№</b><br>бита | Наименование бита       | Функциональное назначение бита, краткое описание бита назначения и принимаемых значений          |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| 31               | INTR_SRC_ENABLE<br>(RW) | 1 — включение источника прерывания                                                               |

| 30 - 5           | _                       |                                                                                                  |

| 4-0              |                         | номер вектора прерываний от 0 до 31, на который направляется соответствующий источник прерываний |

Микросхема интегральная 5023ВС016 Лист Техническое описание 29 Версия 2.04 от 01.09.2017 г. Подп. № докум. *Д*ата

Таблица 3.3.2 — Номера источников прерываний

| Номер      | Наименование | Номер      | Наименование     | Номер      | Наименование  |

|------------|--------------|------------|------------------|------------|---------------|

| источника  | источника    | источника  | источника        | источника  | источника     |

| прерываний | прерываний   | прерываний | прерываний       | прерываний | прерываний    |

| 1          | 2            | 1          | 2                | 1          | 2             |

| 00         | Watchdog     | 26         | UART 3           | 53         | CAN 2         |

| 01         | Timer 1      | 27         | UART 4           | 56         | EDAC          |

| 03         | Timer 2      | 28         | UART 5           | 98         | DMA SPI 2 TX  |

| 04         | Timer 3      | 29         | UART 6           | 99         | DMA SPI 2 RX  |

| 08         | Timer 4      | 32         | SPI 1            | 100        | DMA UART 1 TX |

| 09         | GPIO A       | 33         | SPI 2            | 101        | DMA UART 1 RX |

| 10         | GPIO B       | 36         | SpaceWire 1      | 102        | DMA UART 2 TX |

| 11         | GPIO C       | 37         | SpaceWire 2      | 103        | DMA UART 2 RX |

| 12         | GPIO D       | 40         | МКПД 1           | 104        | DMA UART 3 TX |

| 13         | GPIO E       | 41         | МКПД 2           | 105        | DMA UART 3 RX |

| 14         | GPIO F       | 42         | МКПД 3           | 106        | DMA UART 4 TX |

| 15         | GPIO G       | 43         | МКПД 4           | 107        | DMA UART 4 RX |

| 16         | GPIO H       | 48         | TMTX             | 108        | DMA UART 5 TX |

| 23         | GPIO I       | 49         | TCRX             | 109        | DMA UART 5 RX |

| 24         | UART 1       | 50         | I <sup>2</sup> C | 110        | DMA UART 6 TX |

| 25         | UART 2       | 52         | CAN 1            | 111        | DMA UART 6 RX |

#### 3.4 Регистры общего назначения

## 3.4.1 Состав регистров общего назначения

Состав регистров общего назначения приведён в таблице 3.4.1.

Назначения разрядов регистров общего назначения приведены в таблицах 3.4.2 - 3.4.38.

Таблица 3.4.1 — Состав регистров общего назначения

| Сме-   | Название регистра | Тип | Значение по сбросу | Описание                                                          |

|--------|-------------------|-----|--------------------|-------------------------------------------------------------------|

| 1      | 2                 | 3   | 4                  | 5                                                                 |

| 0 x 00 | EXTMEM_CTRL       | RW  | 0x1FF              | Конфигурирование контроллера внешней памяти по Chip Select 1      |

| 0 x 04 | EDAC_CTRL         | RW  | 0x3                | Включение режима исправления и детекции ошибок внутренней памяти. |

| 0 x 08 | INTMEM_CERR_CNT   | RO  | 0                  | Счётчик исправленных ошибок внутренней памяти блока 1.            |

| 0 x 0C | INTMEM_FERR_CNT   | RO  | 0                  | Счётчик неисправимых ошибок внутренней памяти блока 1.            |

| Изм | Лист | № докум. | Подп. | Дата |

|-----|------|----------|-------|------|

Инв. № дубл.

Взам. инв. №

Подп. и дата

Микросхема интегральная 5023BC016 Техническое описание Версия 2.04 om 01.09.2017 г.

| 1      | 2                    | 3  | 4     | 5                                                                |

|--------|----------------------|----|-------|------------------------------------------------------------------|

| 0 x 10 | EXTMEM_CERR_CNT      | RO | 0     | Счётчик исправленных ошибов внешней памяти.                      |

| 0 x 14 | EXTMEM_FERR_CNT      | RO | 0     | Счётчик неисправимых ошибо внешней памяти.                       |

| 0 x 1C | SPACEWIRE_CLK_CTRL   | RW | 0     | Выбор тактовой частоты блоко SpaceWire                           |

| 0 x 20 | INTMEM2_CERR_CNT     | RO | 0     | Счётчик исправленных ошибов внутренней памяти блока 2.           |

| 0 x 24 | INTMEM2_FERR_CNT     | RO | 0     | Счётчик неисправимых ошибо внутренней памяти блока 2.            |

| 0 x 28 | PWR_CTRL_CLK         | RW | 0     | Включение тактовых частот различных блоков                       |

| 0 x 2C | PWR_CTRL_RST         | RW | 0     | Асинхронный сброс различных блоков                               |

| 0 x 30 | EXTMEM2_CTRL         | RW | 0x1FF | Конфигурирование контроллер внешней памяти по Chip Select        |

| 0 x 34 | EXTMEM3_CTRL         | RW | 0x1FF | Конфигурирование контроллер внешней памяти по Chip Select        |

| 0 x 38 | EXTMEM4_CTRL         | RW | 0x1FF | Конфигурирование контроллер внешней памяти по Chip Select        |

| 0 x 3C | CACHE_HIGH_ADDR      | RW | 0     | Задает пространство работы кэ                                    |

| 0 x 40 | INTMEM_SCR_RNG_ADDR  | RW | 0x3   | Диапазон адресов скраббера дл<br>блока памяти 1.                 |

| 0 x 44 | INTMEM_SCR_PRD_SCAN  | RW | 0     | Период сканирования скраббер для блока памяти 1.                 |

| 0 x 48 | INTMEM_SCR_PRD_STOP  | RW | 0     | Период прерывания скрабберо контроллер памяти 1.                 |

| 0 x 4C | INTMEM2_SCR_RNG_ADDR | RW | 0x3   | Диапазон адресов скраббера дл<br>блока памяти 2.                 |

| 0 x 50 | INTMEM2_SCR_PRD_SCAN | RW | 0     | Период сканирования скраббер для блока памяти 2.                 |

| 0 x 54 | INTMEM2_SCR_PRD_STOP | RW | 0     | Период прерывания скрабберо контроллер памяти 2.                 |

| 0 x 58 | INTMEMS_SCR_MAIN     | RW | 0     | Общее управление скрабберам                                      |

| 0 x 5C | CACHE_CRC_ERROR      | RO | 0     | Счётчик сгс ошибок в кэше                                        |

| 0 x 60 | EDAC_INTMEM_SCR_CERR | RO | 0     | Счётчик исправимых ошибок, обнаруженных скраббером бло памяти 1. |

Изм Лист № докум. Подп. Дата

Инв. № дубл.

Взам. инв. №

Подп. и дата

Инв. № подл.